Hier jetzt mal die allgemeinen Aufbauhinweise ...

Jeder sollte sich mal den/die c´t Artikel von Heise besorgen ->

https://shop.heise.de/archiv/search/result?query=tausch+mit+turboLeserliche Schaltpläne als PDF kann ich per Anfrage via eMail verschicken ...

Die Bauteile sind so benannt wie im original von neogain, also kann man nach der original Bestückungsliste gehen. Die wichtigsten Bauteile bei Kessler sind ...

- M0204 560R (Widerstand 3mm 1%)

- M0204 1k

- M0204 4,7k

- M0204 10k

- QOS 32,000Mhz (optionaler Quarz FPU)

- PGA114 (Sockel 68020

- PLCC68Z (Sockel FPU)

- PZF64 (IC Fassung 68000)

- PZF20, PZF24, PZF14, PZF32

- TAN 10/16

- KER 22P R2,5

- VS 100N Z5U 2,5 (100nF Kondensator)

- JUMPER2,54-SW

- SA32SIL (68000 Pfostenleiste)

- STL1x50G (Jumper Pfostenleisten)

- 27C512 (Eprom 64kB 4 Stk. für TOS 2.06)

- GAL 20V8-15ns

- GAL 16V8-15ns

- MC68020RC20E (knapp 30,- Euro)

FPU ->

http://www.vesalia.de/d_68882.htmDurch die Patches wird die Platine schon mit dem FPU Sockel und den 68000 Sockeln+Pfostenleiste und 2Stk. 24pol. GAL Sockeln geliefert. Da ich in einer Versandtasche als Brief versende ist zum Schutz der 68000 Pfostenleiste ein 64pol. Sockel der wahrscheinlich beim Transport kaputt geht aber das macht nichts. Die goldene 68000 Pfostenleiste ist sehr empfindlich also Vorsicht beim Handieren damit. Später beim Einbau muss sowiesso ein Türmchen aus 64pol. IC Sockeln gebaut werden, also genügend bestellen.

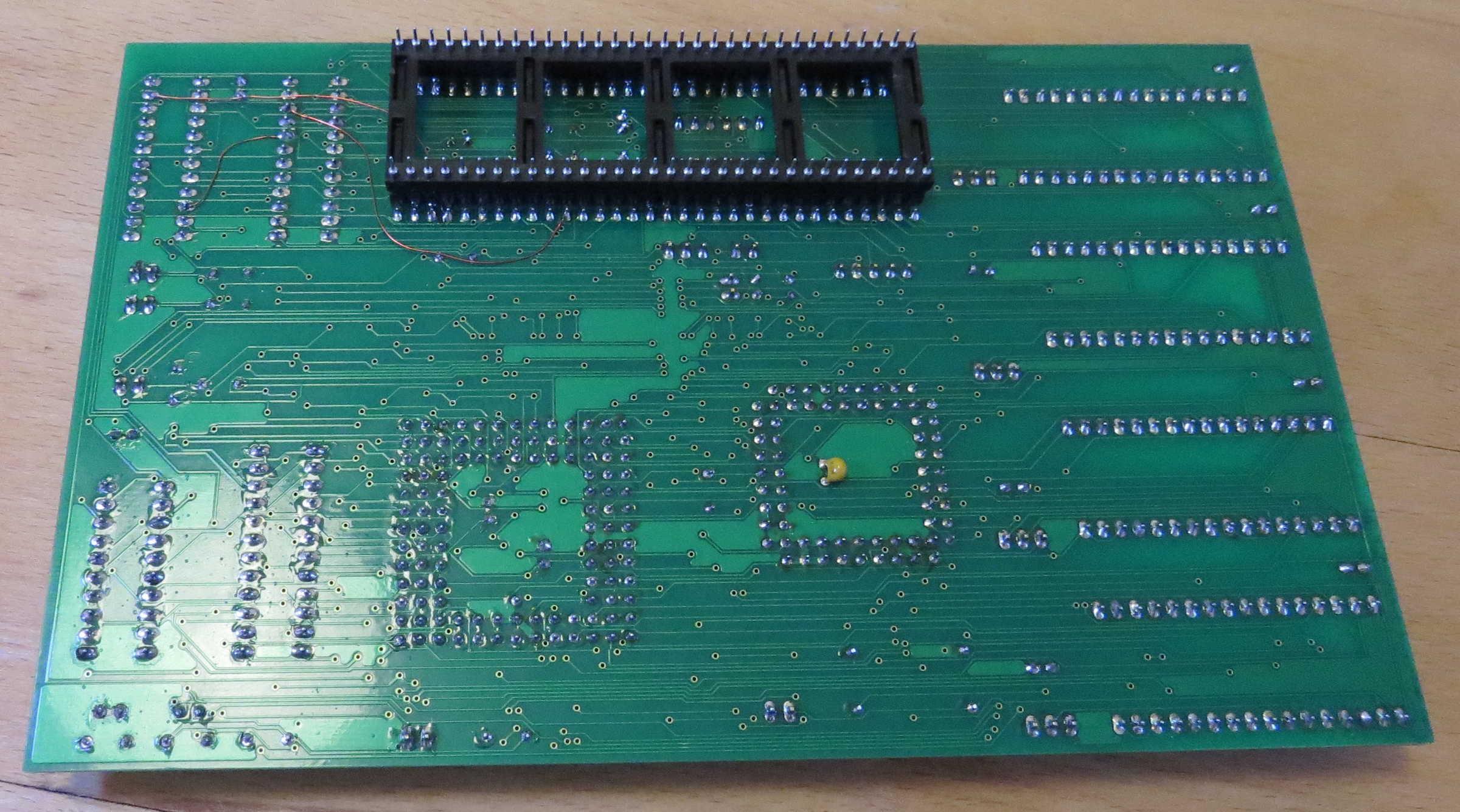

Alle Bauteile werden normal auf der Bauteilseite bestückt bis auf den Kondensator für die FPU. Anbei auch zwei Bilder an denen man sich orientieren kann.

Hier das Splitfile um aus dem normalen TOS 2.06 Image die vier Eprom Files für das 32-bit breite TOS für die PAK zu erzeugen. Benutzt wird das Romslit Paket aus dem Pinatubo Programm Paket. Es gibt ja auch noch das TOSPatch von Markus Heiden um Anpassungen am TOS umzusetzen ...

# Kommandodatei fr ROMMIX:

# erstellen von 4 Eprom-Files fr 27C512

# 1 TOS-IMG wird auf 4 Eproms aufgeteilt

# von Udo Overath @ KR

# (das geht auch direkt mit Pinatubo --- ms)

# Puffergre setzen

bufsize 256k

# Directory setzen

chdir a:\pinatu24\rommix\

load tos206.img 0 256k all -> 0 all

save ee.u11 64k <- 0 ee

save oe.u10 64k <- 0 oe

save eo.u9 64k <- 0 eo

save oo.u8 64k <- 0 ooWer den GAL Satz selber macht sollte beim programmieren Nullbytes = 00 setzen. Hier im Anhang sind die JED Files zu den GAL Bausteinen.

Die PAK68/2 läuft wunderbar zusammen mit der MonSTer Erweiterung von Alan. Auf der MonSTer muss nur ein TOS 1.04 oder KAOS TOS eingestellt sein, damit die PAK mit Ihrem TOS 2.06 booten kann. Die PAK68/2 braucht ein kleines TOS unter/gleich 1.04 auf dem Mainboard.